- 您现在的位置:买卖IC网 > Sheet目录3831 > PIC18F4423-I/ML (Microchip Technology)IC PIC MCU FLASH 8KX16 44QFN

2009 Microchip Technology Inc.

DS39755C-page 41

PIC18F2423/2523/4423/4523

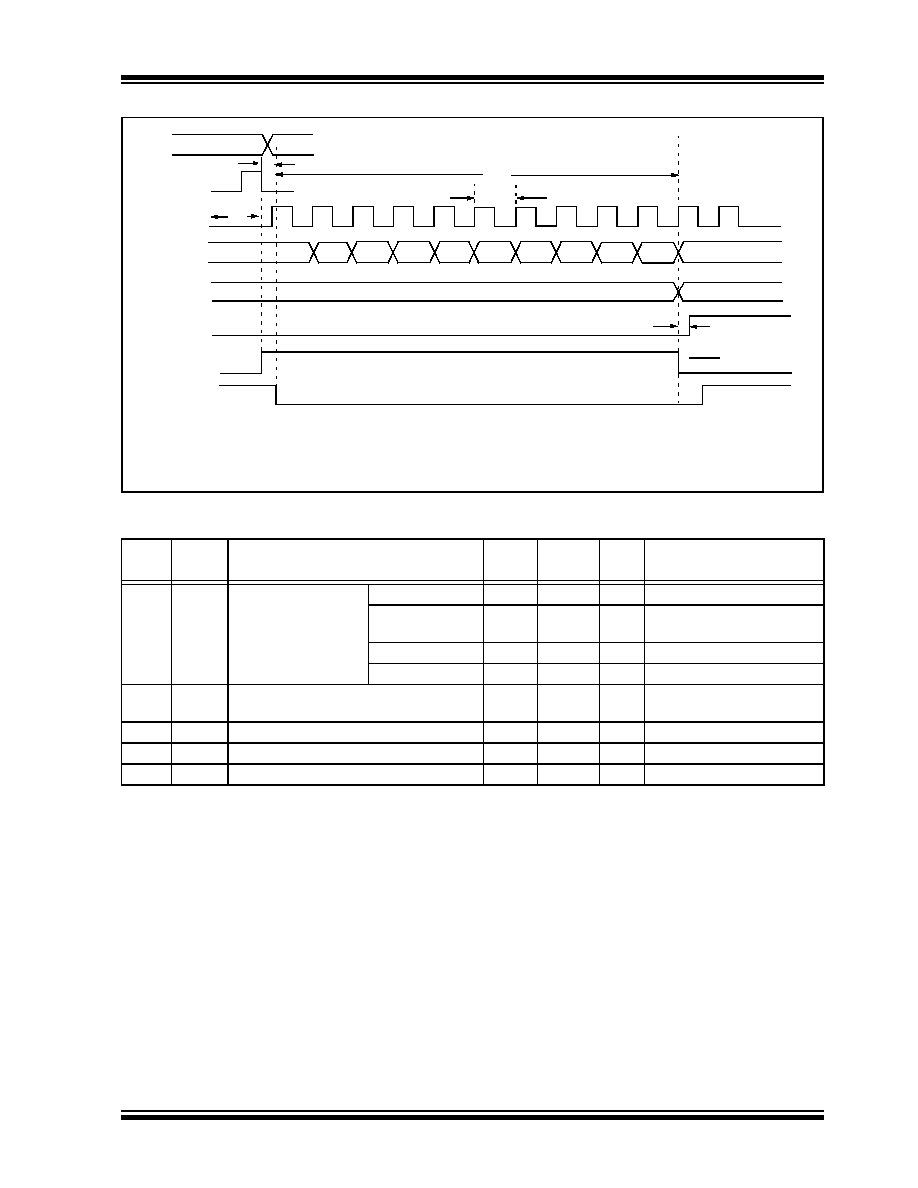

FIGURE 4-4:

A/D CONVERSION TIMING

TABLE 4-2:

A/D CONVERSION REQUIREMENTS

Param

No.

Symbol

Characteristic

Min

Max

Units

Conditions

130

TAD

A/D Clock Period

PIC18FXXXX

0.8

12.5(1)

μsTOSC based, VREF ≥ 3.0V

PIC18LFXXXX

1.4

25.0(1)

μsVDD = 3.0V;

TOSC based, VREF full range

PIC18FXXXX

—

1

μs

A/D RC mode

PIC18LFXXXX

—

3

μsVDD = 3.0V; A/D RC mode

131

TCNV

Conversion Time

(not including acquisition time)(2)

13

14

TAD

132

TACQ

Acquisition Time(3)

1.4

—

μs

135

TSWC

Switching Time from Convert

→ Sample

—

(Note 4)

137

TDIS

Discharge Time

0.2

—

μs

Note 1: The time of the A/D clock period is dependent on the device frequency and the TAD clock divider.

2: ADRES registers may be read on the following TCY cycle.

3: The time for the holding capacitor to acquire the “New” input voltage when the voltage changes full scale

after the conversion (VDD to VSS or VSS to VDD). The source impedance (RS) on the input channels is 50

Ω.

4: On the following cycle of the device clock.

131

130

132

BSF ADCON0, GO

Q4

A/D CLK(1)

A/D DATA

ADRES

ADIF

GO

SAMPLE

OLD_DATA

SAMPLING STOPPED

DONE

NEW_DATA

(Note 2)

11

10

9

3

2

1

Note 1:

If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This allows the SLEEP instruction

to be executed.

2:

This is a minimal RC delay (typically 100 ns), which also disconnects the holding capacitor from the analog input.

. . .

TCY

0

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16F874A-I/P

IC MCU FLASH 4KX14 EE 40DIP

PIC18F87J60-I/PT

IC PIC MCU FLASH 64KX16 80TQFP

PIC24HJ128GP202-I/MM

IC PIC MCU FLASH 128K 28-QFN

PIC16F873-04/SO

IC MCU FLASH 4KX14 EE 28SOIC

PIC24FJ128GA106-I/PT

IC PIC MCU FLASH 64TQFP

AT87C51RD2-RLTUM

IC 8051 MCU 64K OTP 40MHZ 44VQFP

AT87C51RD2-RLTUL

IC 8051 MCU 64K OTP 30MHZ 44VQFP

PIC16F873-04/SP

IC MCU FLASH 4KX14 EE 28DIP

相关代理商/技术参数

PIC18F4423-I/P

功能描述:8位微控制器 -MCU 16KB 768bytes-RAM 36I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4423-I/PT

功能描述:8位微控制器 -MCU 16KB 768bytes-RAM 36I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4423-I/PT

制造商:Microchip Technology Inc 功能描述:8-Bit Microcontroller IC

PIC18F4423T-I/ML

功能描述:8位微控制器 -MCU 16KB 768bytes-RAM 36I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4423T-I/PT

功能描述:8位微控制器 -MCU 16KB 768bytes-RAM 36I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F442-E/L

功能描述:8位微控制器 -MCU 16KB 768 RAM 34I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F442-E/ML

功能描述:8位微控制器 -MCU 16KB 768 RAM 34I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F442-E/P

功能描述:8位微控制器 -MCU 16KB 768 RAM 34I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT